In this article, I have tried to collect I2C Interview questions which can ask by your Interviewer. I have already written an article on I2C protocol if you have not seen this article, you should read this article before starting this Q&A.

I2C Interview Questions :

Q1 : What is I2C communication?

Ans: I2C (Inter-Integrated Circuit) is a serial communication protocol designed to enable communication between a master and one or more slave devices. It is commonly used to interface with slow-speed peripherals such as EEPROM, ADCs, I2C-based LCDs, RTCs, and more. I2C is not limited to communication on a single board; it also supports external components connected via cables.

I2C is a two-wire protocol, using:

- SDA (Serial Data Line) – for data transfer.

- SCL (Serial Clock Line) – for clock synchronization.

Both the SDA and SCL lines are bidirectional. The master initiates communication and generates the clock signal, but slaves can also influence the clock line through a mechanism called clock stretching, where a slave holds the clock line low to delay the master.

I2C is widely adopted in various control and management architectures, such as:

- SMBus (System Management Bus)

- PMBus (Power Management Bus)

- IPMI (Intelligent Platform Management Interface)

Q2 : What does I2C stand for?

Ans: I2C stands for “Inter-Integrated Circuit.”

Q3 : How many wires are required for I2C communication?

Ans: I2C communication requires only two wires:

- SDA (Serial Data Line)

- SCL (Serial Clock Line)

These two lines handle both data transmission and synchronization between the master and slave devices.

Q4 : I2C is half-duplex or full-duplex?

Ans: I2C is a half-duplex communication protocol. In I2C, data transmission occurs in one direction at a time—either from master to slave or from slave to master.

Q5 : I2C is Synchronous or Asynchronous Communication?

Ans: I2C is synchronous communication. The master generates the clock signal (SCL) to synchronize data.

Q6 : Explain the physical layer of the I2C protocol

Ans: I2C uses a master-slave architecture. It supports multiple masters and slaves, but most systems use one master and one or more slaves.

I2C uses only two lines for communication:

- SDA (Serial Data Line)

- SCL (Serial Clock Line)

All devices connect to the same SDA and SCL lines. These lines use a wired-AND setup with open-drain pins. This allows multiple devices to share the bus without causing signal conflicts.

In open-drain mode, devices can only pull the line low. They cannot drive it high. Pull-up resistors are used to bring the lines high when no device is pulling them low. The value of the pull-up resistors is important. Wrong values can lead to slow signals or failed communication.

Note: Most designs use a single master to keep things simple and avoid bus conflicts.

If you want to learn STM32 from scratch, you should follow this course “Mastering Microcontroller with Embedded Driver Development“. The course contains video lectures of 18.5-hours length covering all topics like, Microcontroller & Peripheral Driver Development for STM32 GPIO, I2C, SPI, USART using Embedded C.

Enroll In Course

Q7 : Explain the operation and frame of I2C protocol

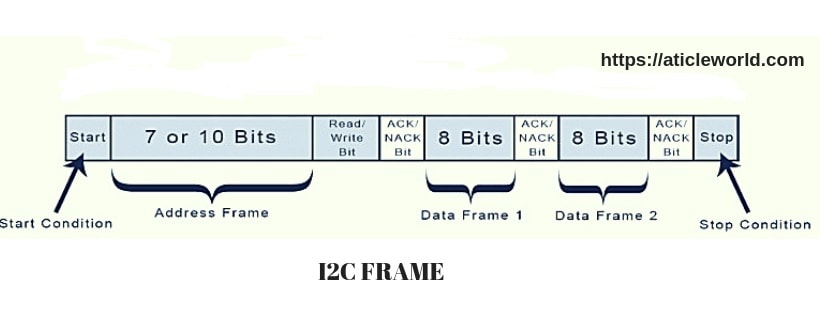

Ans: I2C is a chip-to-chip communication protocol. Communication is always initiated by the master device. To begin communication, the master sends a START signal, followed by the 7-bit or 10-bit slave address and a Read/Write (R/W) bit.

After the START signal, all slaves listen. The slave whose address matches the transmitted address responds by sending an ACK (acknowledgment) bit back to the master.

- If an ACK is received, the master begins data transfer.

- If no slave matches the address, the master receives a NACK (not acknowledged) and can either:

- Send a STOP condition to end communication, or

- Send a REPEATED START condition to initiate a new communication cycle.

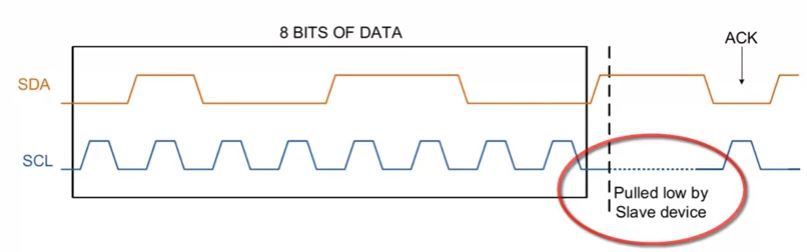

During communication, each byte (whether data or address) is followed by an ACK or NACK bit to confirm successful transmission.

In I2C, one bit is transmitted per clock pulse. Each byte can be:

- A device address

- A register address

- Or actual data being written to or read from the slave

The SDA (data line) must remain stable when the SCL (clock line) is high. Changes on the SDA line are allowed only when the clock is low, except during special conditions:

- START condition: SDA goes low while SCL is high

- STOP condition: SDA goes high while SCL is high

- Repeated START: Another START without sending a STOP in between

Consider the below image,

Q7 : What is START bit?

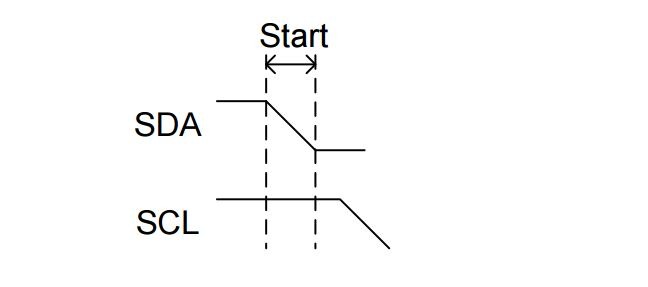

Ans: The default (idle) state of both SDA and SCL lines is high. To begin communication, the master generates a START condition.

A START condition occurs when the SDA line transitions from high to low while the SCL line is high. Only the master can generate the START condition.

Once the START condition is detected, the I2C bus is considered busy, and no other master should attempt to take control of the bus until a STOP condition is issued.

🧠 Key Points to Remember:

- Start Condition => SDA goes low while SCL is high that means first pull SDA low then pull SCL low.

- The Start Condition must always be followed by a valid address frame.

- Always generated by the master.

- Marks the start of a message.

- Bus becomes busy until a Stop or repeated Start condition is sent.

Q7 : What is STOP bit?

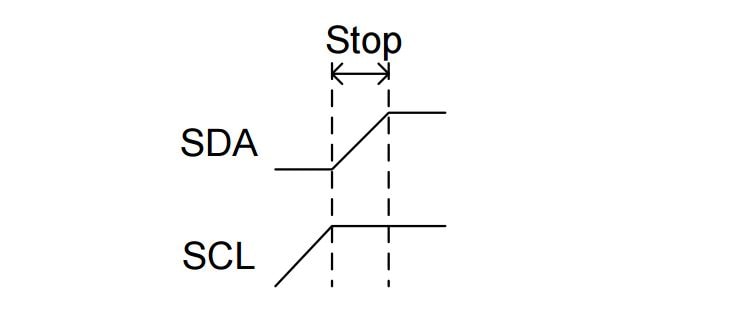

Ans: The STOP condition is used by the master to end the communication on the I2C bus. It occurs when the SDA line transitions from low to high while the SCL line is high. This transition signals the end of the current communication.

Only the master can generate the STOP condition. Once the STOP condition is asserted, the I2C bus is considered free, and other masters (if any) can take control of the bus for new communication.

🧠 Key Points to Remember:

- Stop Condition => SDA goes high while SCL is high; that means first SCL returns high then SDA returns high.

- Only the master can generate the STOP Condition.

- Once the STOP Condition is asserted, the I2C bus is considered idle or free. No clock signal.

- Slave devices return to their waiting state, ready for the next START Condition

Q7 : What is the repeated start condition?

Ans: The Repeated Start condition is similar to the START condition but used in a different context.

It is generated by the master without first issuing a STOP condition, meaning the bus is not idle. This allows the master to maintain control of the bus and initiate a new communication sequence without releasing the bus.

A Repeated Start is useful when the master wants to:

- Communicate with another slave.

- Change the direction of communication (e.g., from write to read).

- Avoid bus arbitration with other masters.

- Only the master can generate a Repeated Start.

Note: Repeated Start is especially useful in systems with multiple masters, where releasing the bus (by sending a STOP) could allow another master to take control.

Q8 : What is the standard bus speed in I2C?

Ans: I2C supports multiple speed modes, each suited for different use cases and hardware capabilities:

| MODE | SPEED |

| Standard-mode | 100 kbit/s |

| Fast-mode | 400 kbit/s |

| Fast-mode Plus | 1 Mbit/s |

| High-speed mode | 3.4 Mbit/s |

| Ultra-Fast mode | 5 Mbit/s |

Note: Ultra Fast-mode (UFm) is a unidirectional (write-only) mode of I2C that supports bit rates of up to 5 Mbit/s. It is typically used in applications where the master only needs to send data to the slave, and no acknowledgment (ACK/NACK) is required.

Q9 : What is the limiting factor as to how many devices can go on the I²C bus?

Ans: The primary limiting factor is the total bus capacitance. According to the I²C specification, the total capacitance on the bus should not exceed 400 pF.

This capacitance includes:

- PCB traces.

- Cable length.

- Device input capacitance.

Exceeding this limit can cause slow signal rise times, data errors, and timing issues.

🔧 To reduce capacitance:

- Keep traces short.

- Use proper pull-up resistors.

- Add bus buffers for longer or more complex setups.

Q10 : Who sends the START bit in I²C?

Ans: The master always sends the START bit to initiate communication on the I²C bus.

Q11 :What is the maximum bus length of the I2C bus?

Ans: The maximum bus length depends on the bus capacitance and communication speed. I²C is not designed for long-distance communication and is typically limited to a few meters.

According to the NXP I²C specification (UM10204):

- For Fast-mode (400 kHz), the total bus capacitance should be below 400 pF, but performance is better under 200 pF.

📏 Example:

If the cable has 20 pF per 25 cm and there is 80 pF of device/stray capacitance, the total length is roughly 1.5 meters. This is just an estimate — actual performance may vary based on layout, wire quality, and shielding.

Q12 : How many kinds of addressing structures are there in I2C?

Ans: I²C supports two types of addressing formats:

- 7-bit addressing (most commonly used)

- 10-bit addressing (for systems with many devices)

Q13 : Is it possible to have multiple masters in I2C?

Ans: Yes, I²C supports multiple masters as well as multiple slaves on the same bus. In a multi-master setup, devices must handle bus arbitration and clock synchronization to avoid conflicts when two masters try to control the bus at the same time.

Q14 : What is a bus arbitration?

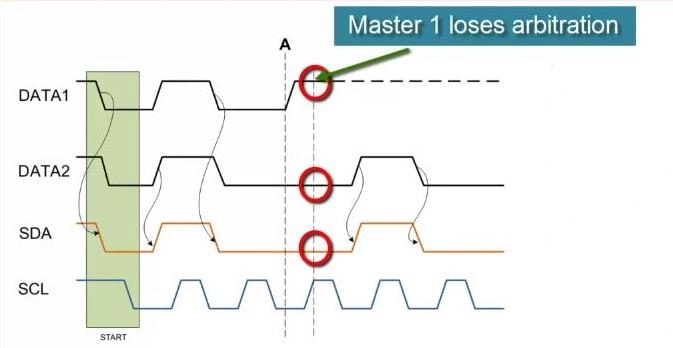

Ans: Bus arbitration is required in multi-master I²C systems, where two or more masters may try to initiate communication at the same time. I²C handles arbitration using the SDA (data) line.

Example:

If two masters try to communicate simultaneously, they both generate a START condition and begin transmitting. The SCL (clock) line is already synchronized due to the wired-AND configuration.

As they transmit data bit-by-bit, each master also monitors the SDA line:

- If a master detects that the actual SDA line is different from the bit it is sending, it knows another master is driving the line.

- It loses arbitration and stops transmitting, allowing the winning master to continue.

Note: The master that loses arbitration waits until the bus becomes free before attempting to communicate again.

Q15 :What is I2C clock stretching?

Ans: Clock stretching is a mechanism in I²C where the slave device holds the SCL (clock) line low to pause communication. The master cannot continue transmission until the slave releases the SCL line and it goes high again.

In normal I2C communication, the slave receives data at the speed controlled by the master. However, if the slave needs more time to process received data, it can pull the SCL line low to delay the next clock pulse.

Once ready, the slave releases the SCL line, allowing communication to resume.

Important Points need to remember:

- Clock stretching allows slower slaves to keep up with faster masters.

- While not all slaves implement clock stretching, every I²C master must support it to ensure compatibility.

Q16 : What is I2C clock synchronization?

Ans: Unlike RS-232, I²C is a synchronous communication protocol, where the clock is always generated by the master and shared with the slave. In a single-master system, synchronization is straightforward since only one clock source exists.

However, in a multi-master system, each master generates its own clock. When two or more masters try to communicate at the same time, clock synchronization becomes necessary.

This leads to the question: How is clock synchronization achieved?

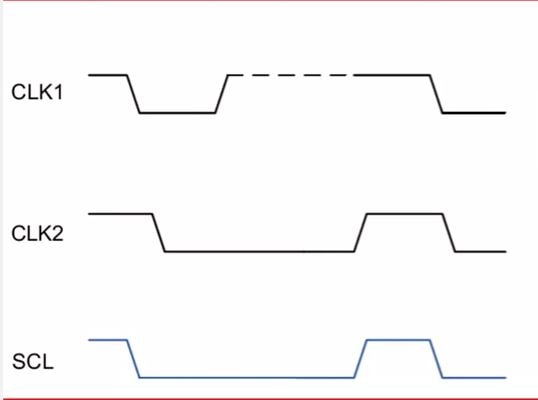

I²C handles this automatically using wired-AND logic on the SCL (clock) line. All masters drive the line through open-drain outputs, and the actual clock on the bus is determined by the logical AND of all the masters’ clocks.

Example:

- Master M1 generates clock clk1

- Master M2 generates clock clk2

- The resulting bus clock SCL = clk1 AND clk2

This means the low period dominates, and the slowest clock wins. The SCL line goes high only when all masters release it (i.e., all clocks are high).

Q17 : When must data be stable for a correct I²C bus transaction?

Ans: In I²C communication, data on the SDA line must remain stable while the SCL line is high. Data should change only when the SCL line is low. If the SDA line changes while SCL is high, it’s treated as a start or stop condition.

Q18 :Is Hot swapping possible in I2C protocol?

Ans: Yes, hot swapping is possible in I²C.

However, it requires careful hardware design. Devices must avoid disrupting the bus when being plugged in or removed.

To support hot swapping safely in I²C systems:

- Use ESD protection diodes and series resistors on SDA and SCL lines to protect against voltage spikes and inrush current.

- Ensure the SDA and SCL pins are in a high-impedance state (Hi-Z) during power-up and connection to avoid affecting the bus.

- Implement bus monitoring and recovery logic (e.g., reset logic or watchdogs) to detect and clear any bus lock-up or stuck-low conditions caused during hot plug.

Q19 : Can devices be added and removed while the system is running in I2C?

Ans: Yes, devices can be added or removed while the system is running because hot swapping is supported in I2C.

Q20 : Which is better to use I2C or SPI?

Ans: Both I2C and SPI have their own advantages and disadvantages. It’s not accurate to say one is always better than the other. The choice depends on the specific requirements of the project.

- SPI offers faster speeds, full-duplex communication, and is better for short-distance, high-speed data exchange.

- I2C uses fewer wires, supports multi-master setups, and is better for communication between multiple peripherals.

You should choose the protocol based on factors like speed, wiring complexity, number of devices, and power consumption.

👉 For a detailed comparison, refer to this article: SPI vs I2C.

What is the application of the I2C protocol?

It is connected with serial RAM, LCD, EEPROM, and its use within the television sets.

If a slave is servicing an internal interrupt, what will it do to avoid losing data?

The slave will stretch the clock until the interrupt servicing is complete.

Can we monitor the I2C bus?

Yes, we can. There are many analyzers available, you can check this analyzer “Siglent SDS1104X-E “.

Advantages of I2C communication?

There is a lot of advantage of I2C protocol which makes the user helpless to use the I2C protocol in many applications.

- It is the synchronous communication protocol, so there is no need of a precise oscillator for the master and slave.

- It requires only two-wire, one wire for the data (SDA) and other wire for the clock (SCL).

- It provides the flexibility to the user to select the transmission rate as per the requirements.

- In I2C bus, each device on the bus is independently addressable.

- It follows the master and slave relationships.

- It has the capability to handle multiple masters and multiple slaves on the I2C Bus.

- I2C has some important features like arbitration, clock synchronization, and clock stretching.

- I2C provides ACK/NACK (acknowledgment/ Not-acknowledgement) features that provide help in error handling.

What are the limitations of I2C interface?

- Half-duplex communication, so data is transmitted only in one direction (because of the single data bus) at a time.

- Since the bus is shared by many devices, debugging an I2C bus (detecting which device is misbehaving) for issues is pretty difficult.

- The I2C bus is shared by multiple slave devices if anyone of these slaves misbehaves (pull either SCL or SDA low for an indefinite time) the bus will be stalled. No further communication will take place.

- I2C uses resistive pull-up for its bus. Limiting the bus speed.

- Bus speed is directly dependent on the bus capacitance, meaning longer I2C bus traces will limit the bus speed.

What is the difference between SPI and I2C (I2C vs SPI)?

You can see this article, Difference between I2c and SPI

Questions for you:

- What is locking(or waiting) and unlocking the I2c protocol? How you could design the unlocking I2c protocol for your system.

- What happens if two devices have the same priority in I2C bus arbitration?

- I2C is Edge Triggering or Level Triggering?

- What is the maximum number of devices that can be connected to an I2C bus?

- Is in I2c two slaves have the same address?

- How will the master indicate that it is either address/data? How will it intimate to the slave that it is going to either read/write?

- What is the voltage level for 0 and 1 in I2C?

- How do I2C devices handle errors and retries during communication?

- How could a slave send the data to the Master in I2C while the master is communicating with another slave?

- How does I2C bus arbitration work?

- What is I2C Multiplexing?

- What is the priority in I2C bus arbitration?

- Why I2C Protocol is Designed?

Recommended Post

- Understanding of I2C protocol.

- SPI vs I2C protocol.

- EEPROM Interfacing with PIC Microcontroller – I2C Based.

- RTC DS1307 Interfacing with PIC Microcontroller.

- Interfacing EEPROM with 8051 Microcontroller – I2C Based.

- 100 embedded C interview Questions.

- 100 C interview Questions.

- I2C interview Questions

- Interview questions on bitwise operators in C

- C++ Interview Questions.

- 10 questions about dynamic memory allocation.

- File handling in C.

- Pointer in C.

- C format specifiers.